# ECT 213 – Lecture 3

Chapter 3

Chapter 5

Logic Gates Truth Tables Boolean Equations

**Logic Gates:** Building blocks for basic digital electronic circuits.

Output will be High (1) or Low(0)

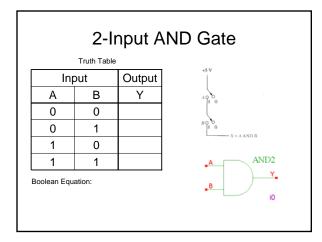

#### Truth Table:

Graphically displays output in table form.

| Example – 2 Input And Gate<br>Timing Diagram |                |                |                |                |                |                |                |                |                |                |  |

|----------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|

|                                              | t <sub>o</sub> | t <sub>1</sub> | t <sub>2</sub> | t <sub>3</sub> | t <sub>4</sub> | t <sub>5</sub> | t <sub>6</sub> | t <sub>7</sub> | t <sub>8</sub> | t <sub>9</sub> |  |

| A                                            |                |                |                |                |                |                |                |                |                |                |  |

|                                              |                |                |                |                |                |                |                |                |                |                |  |

| В                                            |                |                |                |                |                |                |                |                |                |                |  |

| Y                                            |                |                |                |                |                |                |                |                |                |                |  |

# Example – Burglar Alarm

Create a circuit that will sound an alarm when the alarm is armed and the door is opened.

Inputs

Output

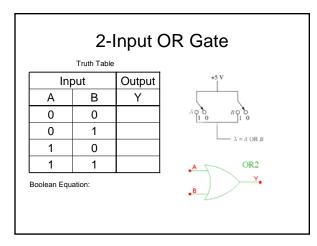

| Exa | xample – 2 Input OR Gate Timing<br>Diagram |                |                |                |                |                |                |                |                |                |   |

|-----|--------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|

|     | t <sub>0</sub>                             | t <sub>1</sub> | t <sub>2</sub> | t <sub>3</sub> | t <sub>4</sub> | t <sub>5</sub> | t <sub>6</sub> | t <sub>7</sub> | t <sub>8</sub> | t <sub>9</sub> |   |

|     |                                            |                |                | -              |                | -              |                | _              |                |                |   |

| A   |                                            |                | T              |                |                |                |                |                |                | -              |   |

|     |                                            |                |                |                |                |                |                |                |                |                |   |

| В   |                                            |                |                |                |                |                |                |                |                |                |   |

|     |                                            |                |                |                |                |                |                |                |                |                | - |

| Y   |                                            |                |                |                |                |                |                |                |                |                |   |

|     |                                            |                |                |                |                |                |                |                |                |                |   |

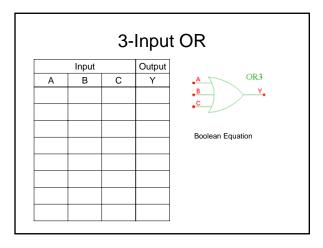

| Exa | Example – 3 Input OR Gate Timing<br>Diagram |                |                |                |                |                |                |                |                |                |

|-----|---------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|     | t <sub>o</sub>                              | t <sub>1</sub> | t <sub>2</sub> | t <sub>3</sub> | t <sub>4</sub> | t <sub>5</sub> | t <sub>6</sub> | t <sub>7</sub> | t <sub>8</sub> | t <sub>9</sub> |

| A   |                                             |                |                |                |                |                |                |                |                |                |

| В   |                                             |                |                |                |                |                |                |                |                |                |

| С   |                                             |                |                |                |                |                |                |                |                |                |

| Y   |                                             |                |                |                |                |                |                |                |                |                |

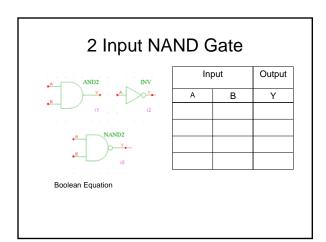

|   | Example – 2 Input NAND Gate<br>Timing Diagram |                |                |                |                |                |                |                | e              |                |                 |

|---|-----------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|

|   | t <sub>o</sub>                                | t <sub>1</sub> | t <sub>2</sub> | t <sub>3</sub> | t <sub>4</sub> | t <sub>5</sub> | t <sub>6</sub> | t <sub>7</sub> | t <sub>8</sub> | t <sub>9</sub> | t <sub>10</sub> |

| A |                                               |                |                |                |                |                |                |                |                |                |                 |

| В |                                               |                |                |                |                |                |                |                |                |                |                 |

| Y |                                               |                |                |                |                |                |                |                |                |                |                 |

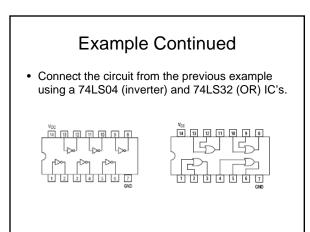

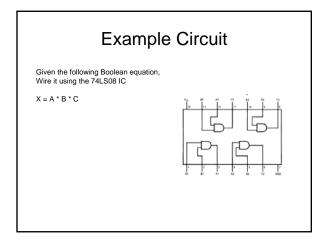

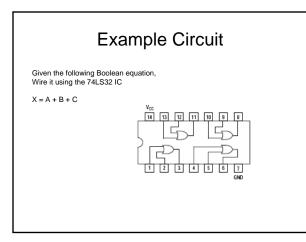

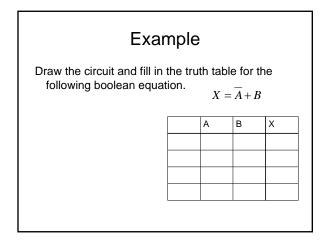

### **Combinational Logic**

Uses one or more basic logic gates to form a function. The Inputs determine the output.

### Examples

Logic for automobile warning buzzer using combinational logic

- Buzzer activates if headlights are on and the driver's door is opened.

- Key is in the ignition and the driver's door is opened

- Motor is running, car in drive and the driver is NOT wearing a seatbelt.

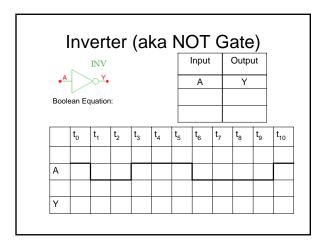

| Comple<br>exampl |                | the            | e tin          | ning           | g di           | agr            | am             | for | the            | e las          | st  |

|------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----|----------------|----------------|-----|

|                  | t <sub>0</sub> | t <sub>1</sub> | t <sub>2</sub> | t <sub>3</sub> | t <sub>4</sub> | t <sub>5</sub> | t <sub>6</sub> | t7  | t <sub>8</sub> | t <sub>9</sub> | t10 |

| A                |                |                | Γ              |                | L              |                |                |     | L              |                |     |

| В                | _              |                |                | Г              |                |                | L              |     |                | F              |     |

| Inverter         | -              | -              |                |                |                |                |                |     |                |                |     |

| Or (X)           | -              | -              |                | -              |                |                |                | -   | -              | -              | -   |